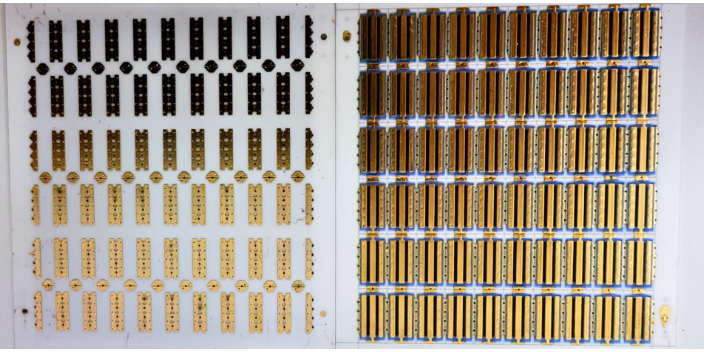

云南薄膜電子元器件鍍金電鍍線

消費電子市場日新月異,消費者對產品的性能、外觀和耐用性要求越來越高,氧化鋯電子元器件鍍金技術為眾多電子產品注入了新的活力。以智能手表為例,其內部的心率傳感器、運動傳感器等部件采用氧化鋯基底并鍍金,氧化鋯的輕薄特性不增加產品額外重量,同時其良好的機械性能能夠適應手腕頻繁活動帶來的微小震動。鍍金層使得傳感器與主板之間的連接更為緊密,信號傳輸更加順暢,確保手表能夠準確監(jiān)測用戶的健康數據,如心率變化、睡眠質量等,并及時反饋給用戶。在虛擬現實(VR)/ 增強現實(AR)設備中,頭戴式顯示器的光學調節(jié)部件、信號傳輸接口等采用氧化鋯并鍍金,既保證了設備在頻繁使用中的耐磨性,又提升了信號的清晰度和穩(wěn)定性,為用戶帶來沉浸式的體驗,滿足人們對智能生活的追求,推動消費電子產業(yè)不斷創(chuàng)新發(fā)展。電子元器件鍍金,可防腐蝕,適應復雜工作環(huán)境。云南薄膜電子元器件鍍金電鍍線

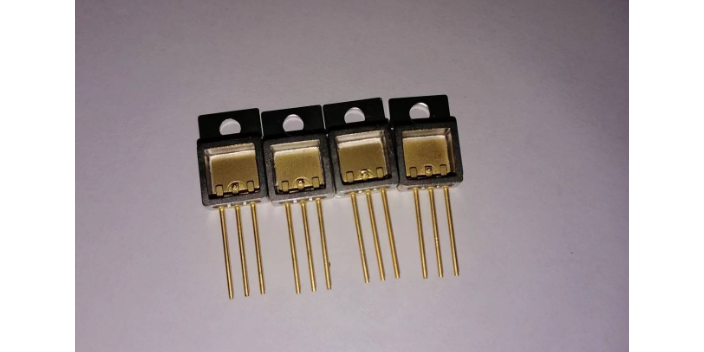

在電子通信領域,5G乃至后續(xù)更先進的通信技術蓬勃發(fā)展,對電子元器件的性能要求達到了前所未有的高度,氧化鋯電子元器件鍍金技術應運而生。在5G基站的射頻前端模塊,功率放大器、濾波器等關鍵部件采用氧化鋯作為基底并鍍金,具有多重優(yōu)勢。氧化鋯的高機械強度能承受基站運行時的輕微振動,確保部件結構穩(wěn)定。鍍金層在高頻段下展現出非凡的低電阻特性,極大地減少了信號的趨膚效應損失,使得5G信號能夠以更強的功率、更遠的距離進行傳播。對于移動終端設備,如5G手機中的天線陣子,氧化鋯的介電性能有助于優(yōu)化天線的輻射效率,鍍金后則提升了天線與芯片之間的連接可靠性,降低信號誤碼率,無論是高清視頻流傳輸、云游戲還是虛擬現實應用,都能讓用戶暢享高速、穩(wěn)定的網絡體驗,是數字時代信息暢通無阻的關鍵推動力。天津管殼電子元器件鍍金銀同遠處理供應商,為電子元器件鍍金保駕護航。

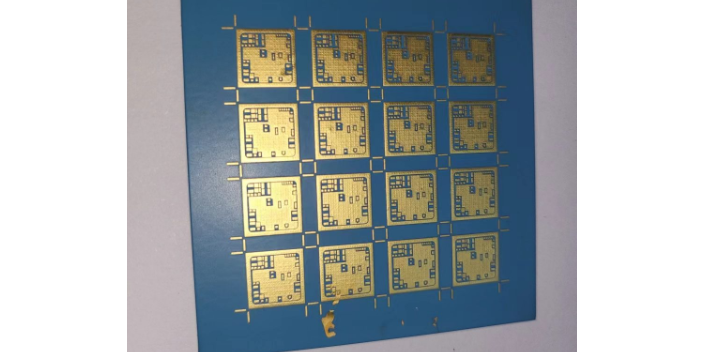

電子元器件鍍金時,金銅合金鍍在保證性能的同時,有效控制了成本。銅元素的加入,在提升鍍層強度的同時,降低了金的使用量,***降低了生產成本。盡管金銅合金鍍層的導電性略低于純金鍍層,但憑借良好的性價比,在眾多對成本較為敏感的領域得到了廣泛應用。實施金銅合金鍍工藝時,前處理要徹底***元器件表面的油污與氧化物,增強鍍層附著力。鍍金階段,精確控制金鹽與銅鹽的比例,一般在6:4至7:3之間。鍍液溫度維持在35-45℃,pH值控制在4.5-5.3,電流密度為0.4-1.4A/dm2。鍍后進行鈍化處理,提高鍍層的抗腐蝕能力。由于成本優(yōu)勢明顯,金銅合金鍍層在消費電子產品的連接器、印刷電路板等部件中大量應用,滿足了大規(guī)模生產對成本和性能的雙重要求。

五金電子元器件的鍍金層本質上是一種電化學防護體系。金作為貴金屬,其標準電極電位(+1.50VvsSHE)遠高于鐵(-0.44V)、銅(+0.34V)等基材金屬,形成有效的陰極保護屏障。通過控制電流密度(1-5A/dm2)和電鍍時間(10-30分鐘),可精確調控金層厚度。在鹽霧測試(ASTMB117)中,3μm厚金層可耐受1000小時以上的中性鹽霧腐蝕,而1μm厚金層在500小時后仍保持外觀完好。在工業(yè)環(huán)境中,鍍金層對SO?、H?S等腐蝕性氣體表現出優(yōu)異抗性。實驗數據顯示,在濃度為10ppm的SO?環(huán)境中暴露720小時后,鍍金層表面產生0.01μm的均勻腐蝕層。對于海洋環(huán)境,采用雙層結構(底層鎳+表層金)可進一步提升防護性能,鎳層厚度需≥5μm以形成致密阻擋層。高精度鍍金工藝,提升電子元器件性能,同遠表面處理值得信賴。

航空航天設備對可靠性有著近乎嚴苛的要求,電子元器件鍍金更是不可或缺。在衛(wèi)星系統(tǒng)里,各類精密的電子控制單元、傳感器等元器件面臨極端惡劣的太空環(huán)境,包括強度高的宇宙射線輻射、巨大的溫度差異(在太陽直射與陰影區(qū)溫度可相差數百攝氏度)以及近乎真空的低氣壓環(huán)境。鍍金層不僅憑借其優(yōu)良的導電性保障復雜電子系統(tǒng)精確無誤地運行指令傳輸,還因其高化學穩(wěn)定性,能阻擋太空輻射引發(fā)的材料老化、性能劣化現象。例如,衛(wèi)星的電源管理模塊中的關鍵接觸點,若沒有鍍金防護,在太空輻射和溫度交變作用下,金屬極易氧化,造成供電不穩(wěn)定,進而威脅整個衛(wèi)星任務的成敗。環(huán)保工藝,高效鍍金,同遠表面處理助力電子制造升級。北京高可靠電子元器件鍍金加工

電子元器件鍍金,同遠處理供應商嚴格把控質量。云南薄膜電子元器件鍍金電鍍線

在5G通信領域,鍍金層的趨膚效應控制成為關鍵技術。當信號頻率超過1GHz時,電流主要集中在導體表面1μm以內。鍍金層的高電導率(5.96×10?S/m)可有效降低高頻電阻,實驗測得在10GHz下,鍍金層的傳輸損耗比鍍銀層低15%。通過優(yōu)化晶粒尺寸(<100nm),可進一步減少電子散射,提升信號完整性。電磁兼容性(EMC)設計中,鍍金層的屏蔽效能可達60dB以上。在印制電路板(PCB)的微帶線結構中,鍍金層的厚度需控制在1.5-2.5μm,以平衡阻抗匹配與成本。對于高速連接器,采用選擇性鍍金工藝(在接觸點局部鍍金)可降低50%的材料成本,同時保持接觸電阻≤20mΩ。云南薄膜電子元器件鍍金電鍍線

- 河南電感電子元器件鍍金產線 2025-04-28

- 福建片式電子元器件鍍金銀 2025-04-28

- 云南薄膜電子元器件鍍金電鍍線 2025-04-28

- 廣東電子元器件鍍金鈀 2025-04-28

- 天津薄膜電子元器件鍍金專業(yè)廠家 2025-04-28

- 陜西貼片電子元器件鍍金電鍍線 2025-04-28

- 北京電子元器件鍍金車間 2025-04-28

- 云南航天電子元器件鍍金加工 2025-04-28

- 北京光學電子元器件鍍金銠 2025-04-28

- 江蘇新能源電子元器件鍍金銠 2025-04-27

- NITTO-VPF110A2-C2防水透氣膜產品 2025-04-28

- LFCG-400+Mini-circuits代理 2025-04-28

- 0.55a可恢復保險絲壓降 2025-04-28

- XB4008AJ電源管理IC代理 2025-04-28

- 珠海汽車線束現貨 2025-04-28

- 黃浦區(qū)通用整流橋售價 2025-04-28

- 蘇州本地處理器價格多少 2025-04-28

- 華東耐高溫成型件公司 2025-04-28

- 福州工廠性能計算機 2025-04-28

- 常見MOS代理商 2025-04-28