湖州I3C邏輯分析儀報價

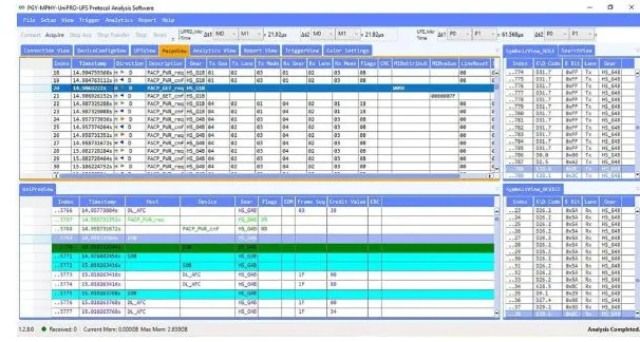

結(jié)果見圖3,在“start”條件后,在SCL的8個連續(xù)脈沖的高電平處,SDA對應的信號為10100010,即0xA2,第9個脈沖高電平處為0,是ACK標志。以上簡單介紹了用邏輯分析儀進行I2C分析的過程,可以看到操作起來非常簡單。下面再介紹利用邏輯分析儀采樣三相交流電機驅(qū)動器的6路PWM波形。硬件連接1.?先將邏輯分析儀的GND與目標板的GND連接,讓二者共地,見圖5。2.?選擇需要采樣的信號,這里就是單片機6路PWM波形的輸出引腳,將其接入邏輯分析儀的通道1(Input1)至通道6(Input6),并且把通道的名字改為Utop、Ubottom、Vtop、Vbottom、Wtop、WBottom,分別三路輸出的上下橋臂。3.?將邏輯分析儀和電腦USB口連接,windows會識別該設備,并在屏幕右下角顯示USB設備標識。軟件使用1.?運行Saleae軟件,此時邏輯分析儀的硬件已經(jīng)與電腦相連,軟件會顯示[Connected]。2.?設置采樣數(shù)量和速度,PWM的頻率為15kHz,這里設置為2MSamples@4MHz的速度。3.?設置觸發(fā)條件,默認“----”就可以了。4.?按“start”按鈕,開始采樣。數(shù)據(jù)分析采樣結(jié)束后。歐奧電子是Prodigy在中國區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測試解決方案不會收到EAR進出口方面的管制。分析儀/訓練器怎么選?找歐奧!湖州I3C邏輯分析儀報價

對于分析高速并行總線就不能勝任了。更進一步的設計,需要增加FPGA、SRAM等器件,才能解決速度不夠和通道數(shù)量不足的問題。圖2圖3圖4下面就以Saleae邏輯分析儀為例,通過采樣分析I2C總線波形和PWM波形,簡單介紹它的特點和使用方法。先介紹用邏輯分析儀采樣單片機對I2C器件AT24C16的寫數(shù)據(jù)過程。硬件連接先將邏輯分析儀的GND與目標板的GND連接,讓二者共地。2.選擇需要采樣的信號,這里就是AT24C16的SDA和SCL,將SDA接入邏輯分析儀的通道1(Input1),SCL接入通道1(Input2)。3.將邏輯分析儀和電腦USB口連接,windows會識別該設備,并在屏幕右下角顯示USB設備標識。軟件使用運行Saleae軟件,此時邏輯分析儀的硬件已經(jīng)與電腦相連,軟件會顯示[Connected]。2.設置采樣數(shù)量和速度,I2C為低速通信,所以速度設置不必太高,這里設置為20MSamples@4MHz的速度,也就是能持續(xù)采樣5秒鐘。3.設置協(xié)議,點右上角的“Options”按鈕,找到analyzer1,設置為I2C協(xié)議,詳見圖1。4.按“Start”按鈕,開始采樣。圖5圖6數(shù)據(jù)分析采樣結(jié)束后,可以看到波形,見圖2。由于我們設置了是I2C分析,因此不光顯示出波形,還有根據(jù)I2C協(xié)議解碼顯示的字節(jié)內(nèi)容。單片機對AT24C16進行寫入操作。湖州EMMC邏輯分析儀電話I3C協(xié)議分析儀/訓練器找歐奧!

作為工程師手頭常備的開發(fā)工具,目前有許多入門級的邏輯分析儀設計,整體功能雖然不能和專業(yè)儀器相比,但是用較低的成本來實現(xiàn)特定的功能,也是非常成功的設計。本文以下討論的邏輯分析儀,主要是指這類入門級設計。基于電腦并口的邏輯分析儀曾是主流,但是近年來電腦系統(tǒng)逐步不再配置并口,這類設計已經(jīng)成為明日黃花,還具有原理學習的價值。另一類的邏輯分析儀,是以低速單片機為基礎的。很多愛好者用PIC、AVR等常見單片機設計了自己的作品。但這類單片機邏輯分析儀的共同弱點就是采樣速度太慢,通常不超過1MHz。以USBIO芯片為基礎的入門級邏輯分析儀現(xiàn)在為流行。比如Saleaelogic,還有類似的USBee等。這類產(chǎn)品主要采用一個USBIO芯片,例如CYPRESS公司的CY7C68013A-56PVXC,所有的信號觸發(fā)和處理工作都是電腦上的軟件完成的,硬件部分就只是一個數(shù)據(jù)記錄儀。高采樣速度為24MHz。它們可以“無限數(shù)量”地采樣,因為所有的數(shù)據(jù)都是存儲在電腦里的。目前一般多是8個通道,更多的通道數(shù)量會成比例地降低高采樣速度。這類產(chǎn)品構(gòu)造簡單,方便易用,價格便宜,是調(diào)試單片機開發(fā)工作的好工具。它的缺點主要是采樣速度只有24MHz、8個通道。

邏輯分析儀基礎邏輯分析儀是一種類似于示波器的波形測試設備,它可以監(jiān)測硬件電路工作時的邏輯電平(高或低),并加以存儲,用圖形的方式直觀地表達出來,便于用戶檢測和分析電路設計(硬件設計和軟件設計)中的錯誤。邏輯分析儀是設計中不可缺少的電子測試設備,通過它可以迅速地定位錯誤、解決問題、達到事半功倍的效果。一、邏輯分析儀的產(chǎn)生和發(fā)展20世紀70年代初研制出微處理器,出現(xiàn)4位和8位總線,傳統(tǒng)示波器的雙通道輸入無法滿足8bit的觀察。微處理器和存儲器的測試需要不同于時域和頻域儀器,所以數(shù)域測試儀器應運而生。當時的HP公司推出狀態(tài)分析儀和Biomation公司推出定時分析儀(兩者初很不相同)之后不久,用戶開始接受這種數(shù)域測試儀器作為終解決數(shù)字電路測試的手段,不久狀態(tài)分析儀與定時分析儀合并成邏輯分析儀。20世紀80年代后期,邏輯分析儀變得更加復雜,使用起來也更加困難。例如,引入多電平樹形觸發(fā),以應付條件語句如IF、THEN、ELSE等復雜事件。這類組合觸發(fā)必然更加靈活,同時對大多數(shù)用戶來說就不是那樣容易掌握了。邏輯分析儀的基本發(fā)展趨勢是計算機與儀器的不斷融合。在PC機平臺上使用Windows,只要給定正確的軟件和相關工具。SD協(xié)議分析儀/訓練器找歐奧!

即使度個樣本符合觸發(fā)條件,邏輯分析儀也只觸發(fā)一次。例如,使用的問題是“如果不符合序列步驟中的條件會怎樣?”例如,有一個條件是“IfADDR=1000ThenTrigger”,那么如果當前樣本是ADDR=2000,結(jié)果會怎樣?邏輯分析儀只采集下一樣本并試圖再次執(zhí)行此序列步驟。實際上,如果觸發(fā)條件是“ADDR=1000”,這相當于“持續(xù)采集樣本直到找到條件為ADDR=1000的樣本”。因此,如果設置一個從不符合的觸發(fā)條件,邏輯分析器將不會觸發(fā)。當符合序列步驟中的條件時,使用“轉(zhuǎn)到”操作時下一步將執(zhí)行哪個序列步驟將會非常清楚,但是如果沒有使用“轉(zhuǎn)到”操作,則不可能知道執(zhí)行哪個序列步驟。在一些邏輯分析儀上,如果沒有“轉(zhuǎn)到”,這意味著應當執(zhí)行下一序列步驟。在其他邏輯分析儀上,意味著將再次執(zhí)行同一序列步驟。由于比較混亂,好使用“轉(zhuǎn)到”操作而不依靠默認。狀態(tài)和定時模塊通過在每個序列步驟中自動包含一個“轉(zhuǎn)到”或“觸發(fā)”操作來解決這一問題。例如:IfADDR=1000andDATA=2000thenGoto1布爾邏輯表達式:當多個序列步驟表示“后跟”時,可以在序列步驟內(nèi)使用布爾邏輯表達式。示例:IfADDR=1000andDATA=2000此表達式意指在同一樣本中ADDR必須等于1000且DATA等于2000。UniPro協(xié)議分析儀/訓練器找歐奧!肇慶I3C邏輯分析儀電話

I3C訓練器協(xié)議分析儀/訓練器找歐奧!湖州I3C邏輯分析儀報價

終比較結(jié)果將對“差分信號高于Vref還是低于Vref?”的問題作出解答:對眼隙的eyescan測量是通過使用不同Vref設置進行一系列eyefinder測量完成的。差分信號的默認eyefinder測量使用Vref=0V。通過將Vref增至零以上。歐奧電子是Prodigy在中國區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協(xié)議分析儀,包括嵌入式設備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓練器,I3C協(xié)議分析儀及訓練器,RFFE協(xié)議分析儀及訓練器等等。我司還有代理SPMI協(xié)議分析儀及訓練器,車載以太網(wǎng)分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件。同時,歐奧電子也有提供高難度焊接,以及高速信號。如UFS,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務。我們會找到信號與上升的Vref值交叉的位置。如果Vref升至足夠高,信號的頂部軌跡將通過Vref,我們便會看到眼的頂端。再將Vref升高一點會導致Vcomp保持在Vlo,表示信號不會升至該電之,將Vref移至零以下會看到眼的下半部。eyescan/eyefinder顯示窗口會在每個信號的eyescan圖下方顯示eyefinder交疊部分,以此顯示eyefinder與eyescan之間的這一關系。湖州I3C邏輯分析儀報價

- 珠海USB協(xié)議分析儀報價 2025-04-29

- 北京UFS協(xié)議分析儀報價 2025-04-29

- 蘇州PCIE協(xié)議分析儀售價 2025-04-29

- 東莞SDIO邏輯分析儀收費 2025-04-29

- 深圳UART協(xié)議分析儀售價 2025-04-29

- 陽江I2C/SPI協(xié)議分析儀那家好 2025-04-29

- 株洲I2C/SPI協(xié)議分析儀費用 2025-04-29

- 長沙EMMC邏輯分析儀收費 2025-04-29

- 佛山I2C/SPI邏輯分析儀報價 2025-04-29

- I2C/SPI協(xié)議分析儀售價 2025-04-29

- 四川手持式多通道紫外成像儀應用范圍 2025-04-29

- 大連光電式編碼器定制價 2025-04-29

- 江蘇高溫高壓導波雷達液位計定做 2025-04-29

- 西安水質(zhì)探頭方案 2025-04-29

- 美國MIRI TL時差培養(yǎng)箱胚胎評分 2025-04-29

- 上海本地負載保持閥平臺 2025-04-29

- 振蕩波局部放電試驗全稱 2025-04-29

- 奧林巴斯x射線熒光礦物檢測元素光譜儀分析儀 2025-04-29

- 50kg電子秤供應商 2025-04-29

- 蘇州剪切試驗機批發(fā)廠家 2025-04-29